- 8 bit parallel in serial out shift register vhdl code pro#

- 8 bit parallel in serial out shift register vhdl code software#

- 8 bit parallel in serial out shift register vhdl code code#

- 8 bit parallel in serial out shift register vhdl code license#

On power-up, if the FPGA detects a valid bitstream stored in the Quad SPI flash memory, the FPGA will Arduino - Serial Peripheral Interface. One conductor is used for data receiving, one for data sending, one for synchronization and one alternatively for selecting a device to communicate with.

8 bit parallel in serial out shift register vhdl code software#

This page is intended to summarize key details related to Xilinx baremetal software for both hardened peripherals within Zynq UltraScale+ MPSoC, Zynq-7000 AP SoC, and embedded IP and IP cores. SPI (Serial Peripheral Interface) is an interface bus commonly used for communication with flash memory, sensors, real-time clocks (RTCs), analog-to-digital converters, and more. Documentation Here is a link to the Xilinx documentation library. Various projects of SPI loader module for xilinx fpga.

8 bit parallel in serial out shift register vhdl code license#

Answers to common licensing questions can be found at our license FAQ section and technical questions on GRLIB-GPL can be posted at the GRLIB.

8 bit parallel in serial out shift register vhdl code pro#

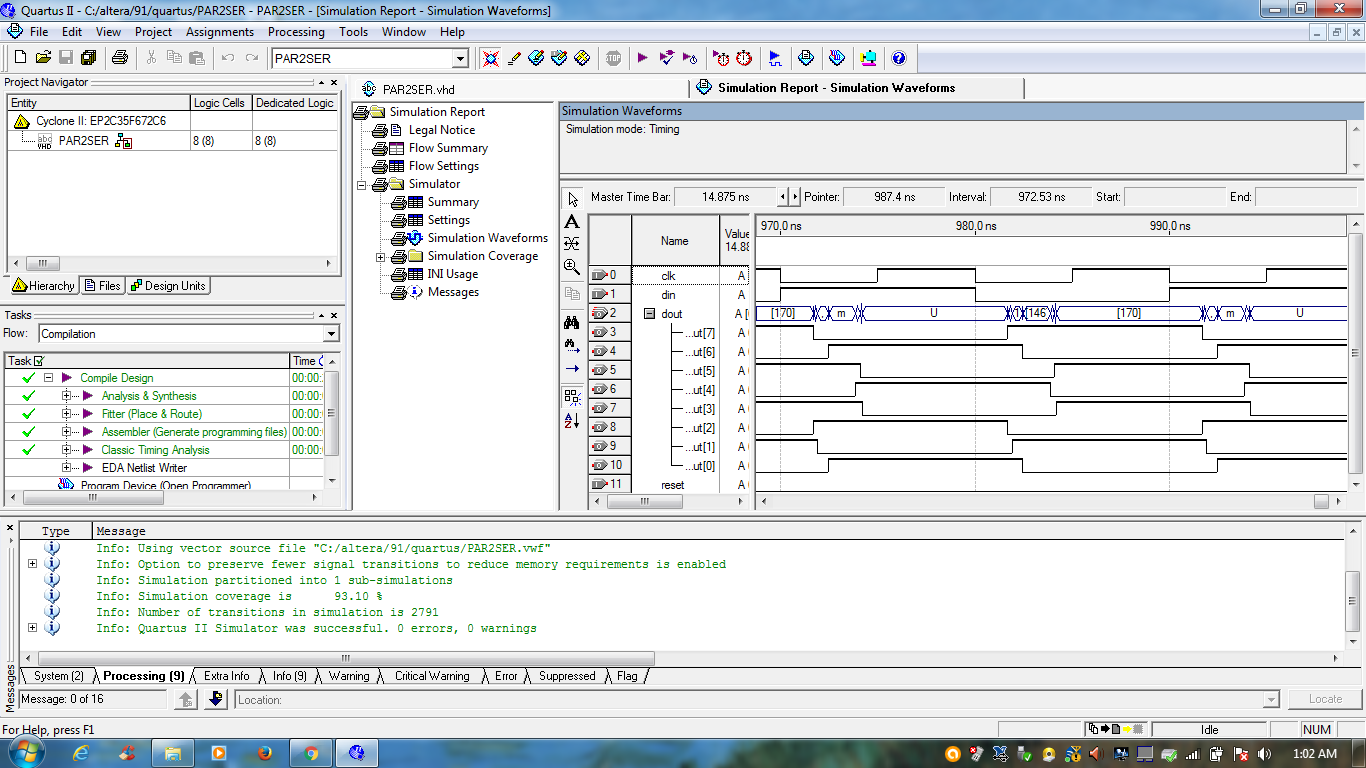

The Lattice iCECube2™ Place and Route tool integrated with Synplify Pro synthesis tool is used for the implementation of the design. SPI (Serial Peripheral Interface) is a four-wire synchronous serial bus. SystemVerilog is a very large and complex language, and the UVM is a large and complex base class library. During logical simulation a patched SecureIP block from Xilinx was used to simulate the MCB's physical part.

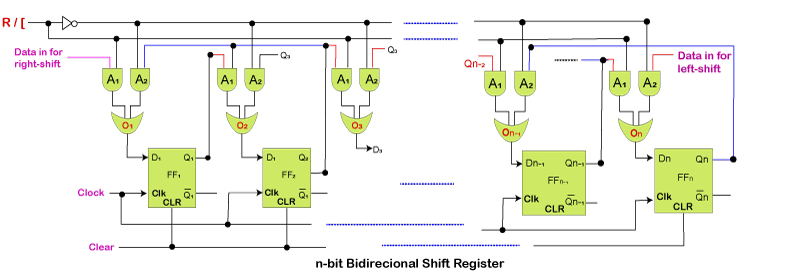

If you are a Xilinx user, use the 'gnuwin' installed as part of the SDK, usually C:\Xilinx\SDK\2019. bit file can be associated with the FPGA by right-clicking on the FPGA icon, selecting the desired. SPI is a protocol used for serial data communication between one master and a couple of slave devices in an embedded world. After this change and a restart of Xilinx SDK the new option will be visible in the BSP settings GUI of the lwip. If you don't see your memory part on this list, our software allows users to add memory devices to the parts library. DINSPI relays the data input from the SPI device when Chapter1 Introduction Overview ThisHDLguideispartoftheVivado™DesignSuitedocumentationcollection. The BootROM inadvertently and unnecessarily enables MIO pin 8 as a toggling output during a Quad-SPI boot sequence. The following circuit is a four-bit Serial in – parallel out shift register constructed by D flip-flops.Xilinx spi library xilinx spi library md test main.

8 bit parallel in serial out shift register vhdl code code#

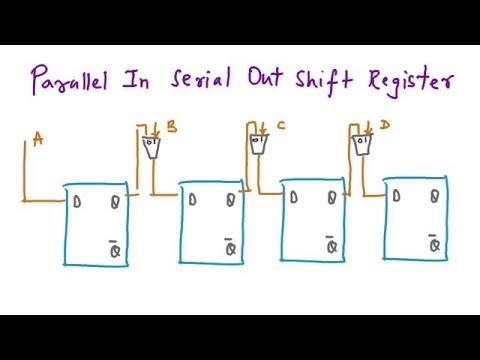

VHDL code for Parallel In Parallel Out Shift Register library ieee Įnd arch Serial In – Parallel Out Shift Registersįor Serial in – parallel out shift registers, all data bits appear on the parallel outputs following the data bits enters sequentially through each flipflop.

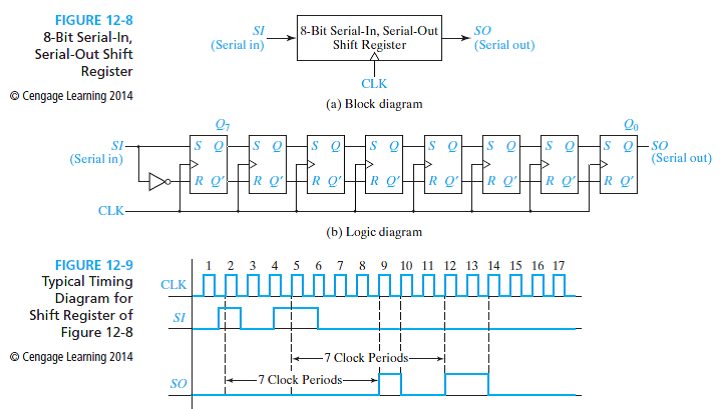

Once the register is clocked, all the data at the D inputs appear at the corresponding Q outputs simultaneously. The D’s are the parallel inputs and the Q’s are the parallel outputs. The following circuit is a four-bit parallel in – parallel out shift register constructed by D flip-flops. Parallel In – Parallel Out Shift Registersįor parallel in – parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits. VHDL Code for shift register can be categorised in serial in serial out shift register, serial in parallel out shift register, parallel in parallel out shift register and parallel in serial out shift register.

0 kommentar(er)

0 kommentar(er)